喜报∣章秀银教授课题组可重构毫米波芯片研究成果分别在CICC会议和JSSC期刊发表

2024-05-14

浏览次数:17872024年4月21日至24日,IEEE定制集成电路设计会议(简称2024 CICC)在美国科罗拉多州丹佛举行。我院博士研究生的可重构毫米波功放芯片研究成果《A Tri-mode Filtering Power Amplifier for 5G Millimeter-Wave Dual-Side LO Injection Systems with Power-Efficiency Enhancement》在该会议上发表。该论文的第一作者2020级博士生曾伟森同学在会议上进行了现场报告,通信作者为章秀银教授,该工作得到了微电子学院高立教授等的指导和支持。

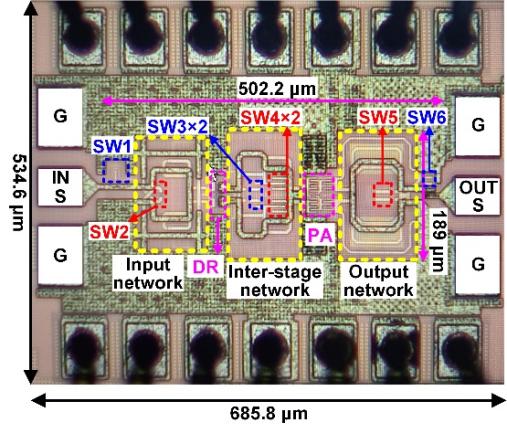

该论文介绍了一种可重构毫米波功放芯片。现阶段主流的毫米波5G频段包括24.25~30GHz和37~43.5GHz,目前流行的超宽带设计方案尽管能覆盖上述频段,但存在镜频干扰、本振泄露和高次谐波问题,且超宽带系统总功耗较高。针对上述问题,论文提出了一种双边LO注入的毫米波5G可重构前端芯片方案,该方案利用LO低于中频和LO高于中频注入方式来覆盖24.25~30GHz和37~43.5GHz频段,仅需窄带LO模块和RF模块,可有效降低系统功耗需求。功率放大器是毫米波通信系统中的关键模块,针对上述频率方案,论文提出了一个工作22~29 GHz、24.6~30.4 GHz和35~45.2 GHz的三模式可重构功率放大器,该功放面积紧凑。设计了基于并联电感的可重构陷波变压器来实现低损耗频段切换,解决了传统基于串联电感的可重构变压器带来损耗过大的问题,同时利用了开关管的关断电容,协同设计陷波功能,从而抑制镜频信号、本振泄露和高次谐波的传输。该功放在效率、抑制干扰信号传输方面具有优势。

图1. 可重构功放芯片显微镜照片

2024年5月,我院硕士研究生的可重构毫米波低噪放芯片研究成果《A Compact Millimeter-Wave Reconfigurable Dual-Band LNA with Image-Rejection in 28-nm Bulk CMOS for 5G Applications》被《IEEE固态电路杂志》(简称JSSC)接收发表,该论文的第一作者是2021级硕士生孙宁政同学,高立教授和章秀银教授为共同通信作者。

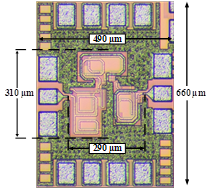

该论文介绍了一种可重构毫米波低噪声放大器芯片。针对毫米波接收机在未来应用场景的跨频段、抗信号干扰、低功耗等需求,论文提出了一个工作于 23.8~33.5 GHz和 34.4~41.4 GHz的双频段可重构低噪声放大器,芯片面积紧凑,适用于5G毫米波接收机系统。该双频段低噪放的级间匹配网络和输出匹配网络采用可重构电容和可重构变压器来切换电路的工作频段,在不增大电路面积和不增加功耗的情况下拓展低噪放的工作带宽。设计了三重磁耦合的可切换变压器以实现频段切换,解决了传统切换结构带来损耗过大的问题,与普通变压器相比几乎不增加额外面积。同时将磁电混合耦合电路与可切换变压器结合,引入一个传输零点来实现镜像频率抑制的同时还使该传输零点位置可切换,以满足低频段和高频段对抗镜频干扰的需求。该低噪放在噪声系数、带宽、功耗和镜频抑制等方面具有优势。

图2. 可重构低噪放芯片显微镜照片

作者介绍:

曾伟森,华南理工大学电子与信息学院通信工程专业2020级博士研究生。获2023年校长奖学金、第六届中国研究生创“芯”大赛全国三等奖以及华为专项二等奖。研究兴趣包括硅基毫米波前端芯片及其关键模块,以第一作者发表JSSC/ISSCC/CICC论文三篇,已授权国家发明专利三项。

作者介绍:孙宁政,华南理工大学电子与信息学院通信工程专业2021级硕士研究生。曾获2023年国家奖学金、第六届中国研究生创“芯”大赛全国三等奖以及华为专项二等奖。研究方向包括硅基毫米波收发机及其关键模块,以第一作者发表JSSC/Trans. CASII论文各一篇,申请国家发明专利两项(已授权一项)。

CICC会议简介:IEEE定制集成电路设计会议(IEEE Custom Integrated Circuit Conference,简称CICC)是芯片设计领域的顶级国际学术盛会之一,自设立以来,CICC每年都吸引着来自世界各地的知名学者、研究人员和工业界代表参与。CICC的论文投稿必须经过评审委员会的多轮严格审核,最终发表的论文代表了学术界和工业界的最新成果、先进设计思想和性能标杆。

JSSC期刊简介:IEEE固态电路期刊(IEEE Journal of Solid-State Circuits,简称JSSC)是集成电路领域公认影响力最大、难度最高的国际顶级期刊,也是中科院JCR分区体系中芯片设计领域唯一的一区期刊。定期发布集成电路领域的最新研究和记录性成果,其中刊发的文章代表了学术界和工业界最先进设计思想和芯片性能标杆。

(文图/戚季,初审/燕维英, 终审/张健 )