研究背景与简介

近年来,可穿戴设备、增强现实和智能手机对高清显示器的需求不断升级,催化了Mini/Micro LED技术的迅速发展。Mini LED芯片的尺寸在100到300 μ m之间,而Micro-LED芯片小于100 μ m 。随着芯片尺寸的减小,现有的封装技术和设备遇到了许多挑战,例如切割精度不足、芯片转移精度不足、效率低、可靠性不足、产量降低和成本升高。扇出封装(FOP)技术是一种先进的半导体封装方法,由于其高密度布线特性,对于Mini/Micro-LED芯片来说非常理想。FOP工艺需要将单个芯片固定到临时载体基板上。由于传输设备的精度有限以及成型过程中包装材料的热膨胀,芯片不可避免地会偏离其设计位置。如果不能实现精确的芯片对准,将导致再分布层(RDL)和芯片电极之间的互连未对准,从而降低器件封装成品率。

激光直写光刻(LDWL)技术是一种灵活的无掩模微/纳米制造技术。通过精确控制激光束,它可以在器件表面上创建微/纳米结构。LDWL非常适合于图案化电极制造。本文提出了一种支持LDWL的FOP方法来自适应LED位置偏差。RDL的LDWL图案基于芯片的实际位置坐标通过机器视觉算法动态生成。

该工作由华南理工大学团队在IEEE Transactions on Semiconductor Manufacturing期刊发表( 10.1109/TSM.2025.3618470),主要由王宙安、刘贺胜等同学完成,指导老师为李家声和李宗涛等。

创新点突出

在这项研究中,我们提出了LED激光直写光刻扇出封装技术,旨在解决扇出封装过程中LED芯片转移引起的位置偏移难题。

重分布层(RDL)图案基于芯片的实际位置生成,可灵活补偿芯片位置偏移,并确保RDL和芯片电极之间的精确对准。

设计并优化了不同的LED-RDL结构,展示了LDWL-FOP方法的高灵活性。

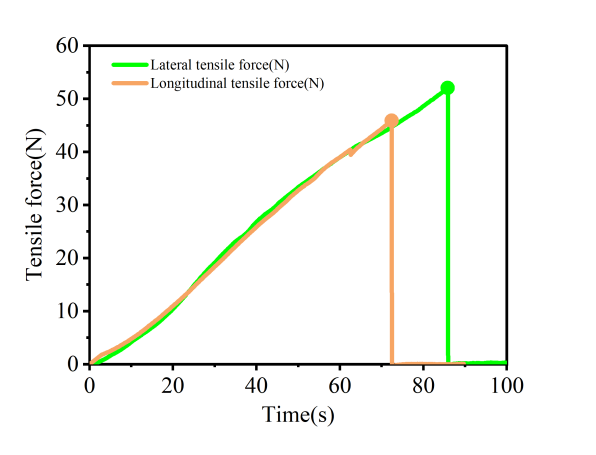

结合磁控溅射与电镀技术制造RDL层,电路结构具备优良的电气性能与机械可靠性,扇出封装LED器件剪切破坏力最高达到50N。

图文导图

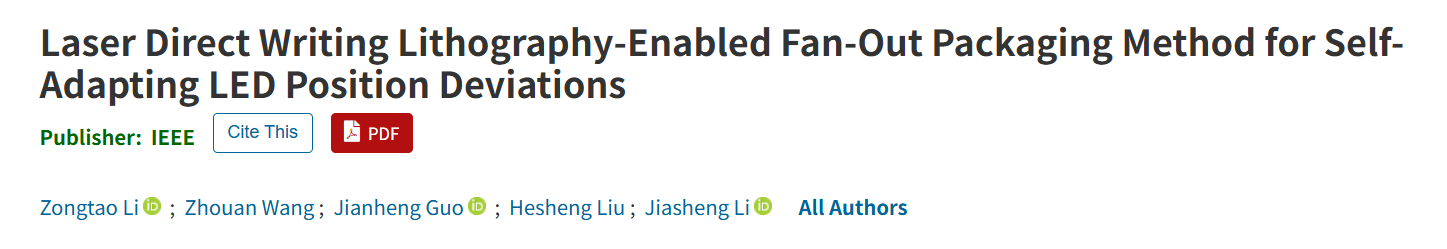

Fig. 1. LDWL-FOP工艺(a)模压工艺。(b)LDWL工艺。(c)RDL制造工艺。

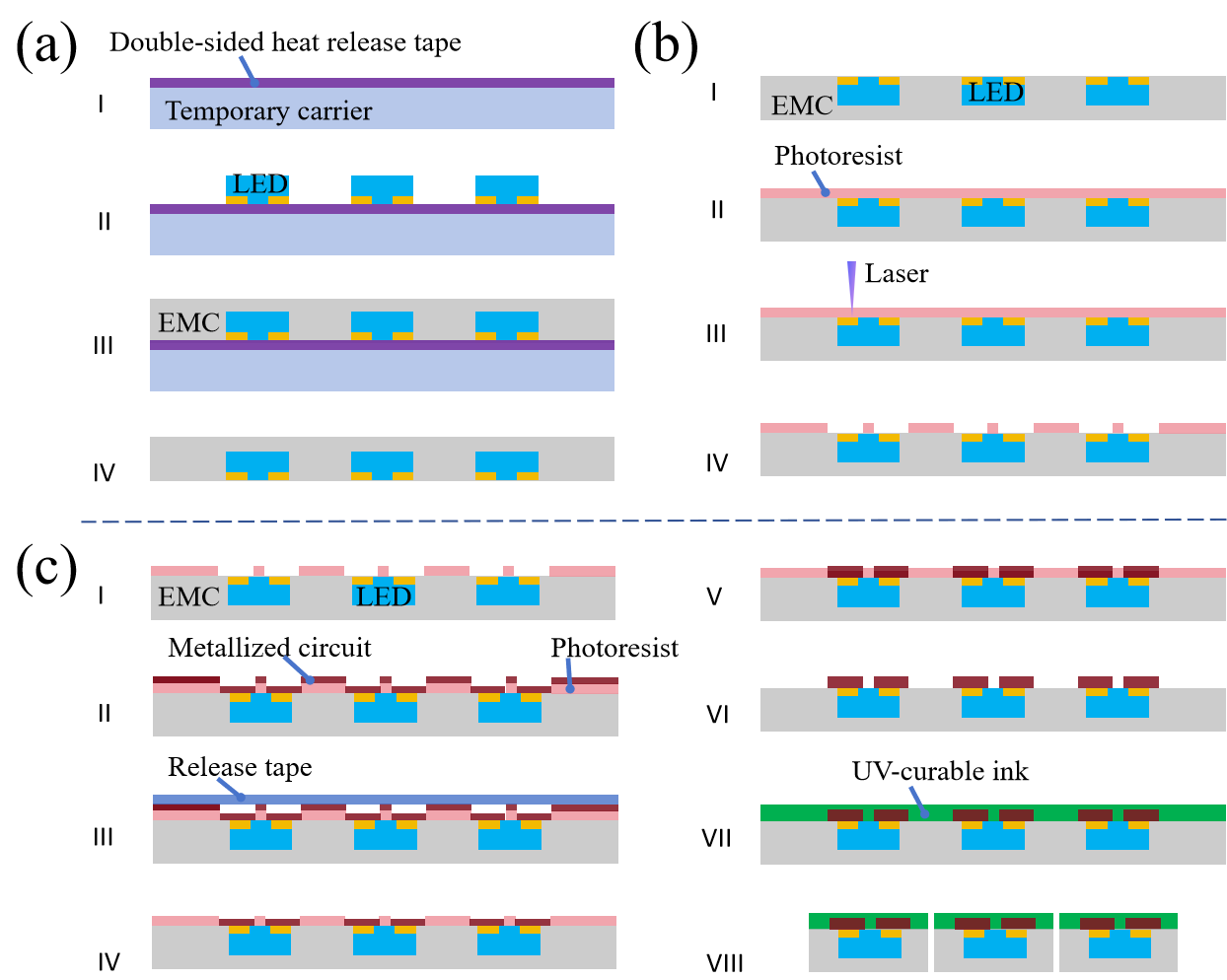

Fig2.LDWL原理图。

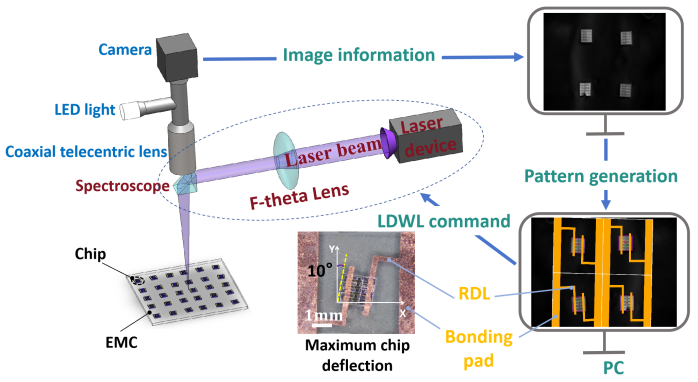

Fig3.在不同LDWL曝光功率下的光刻胶曝光和显影结果。(a)曝光功率为9、18、27和36 mW时的光刻胶曝光和显影效果。(b)在18 mW和27 mW曝光功率下200 μ m宽直角线条的显影结果。

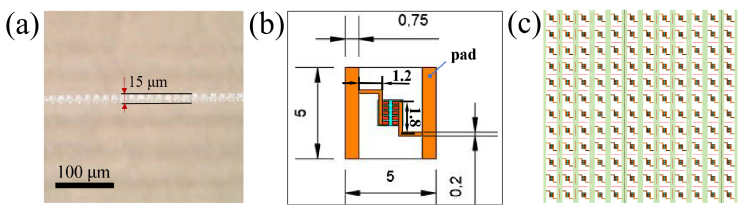

Fig4.(a)曝光后的离散点图像。(b)单个芯片的LDWL图案。(c)面板级FOP。

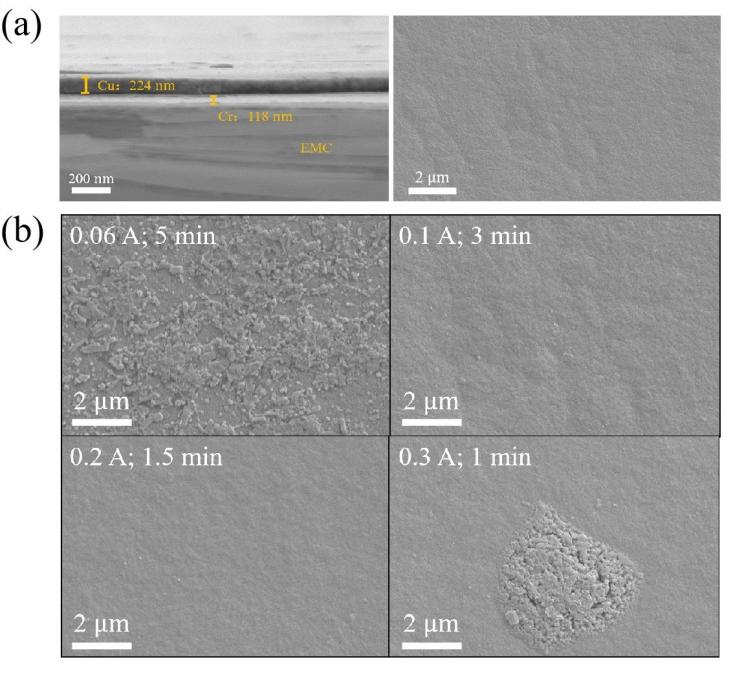

Fig5. (a)磁控溅射金属层的横截面和表面SEM图像。(b)不同电镀工艺参数下镀层的表面形貌。

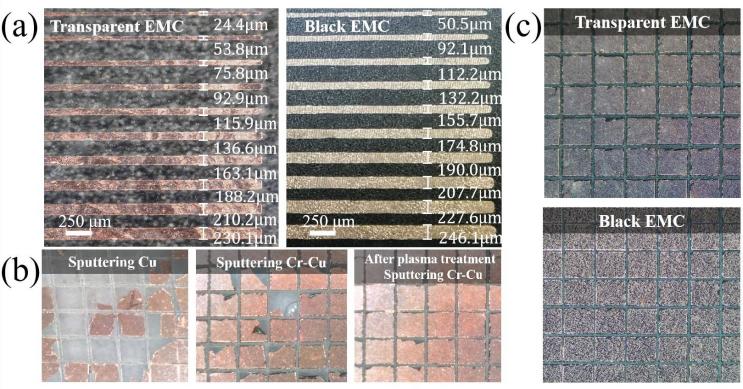

Fig6.(a)在透明和黑色EMC上制备各种线宽的金属电路层。(b)溅射工艺对EMC基板上金属电路附着强度的影响。(c)透明和黑色EMC的网格切割附着力测试结果。

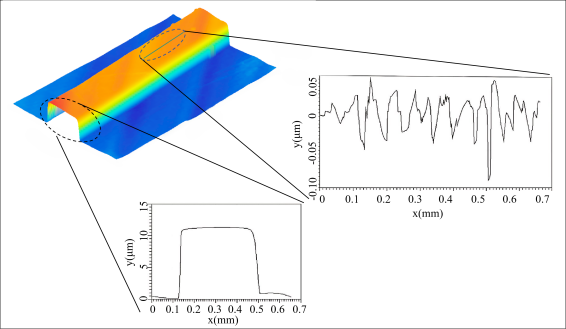

Fig7.RDL的3D光学轮廓图。

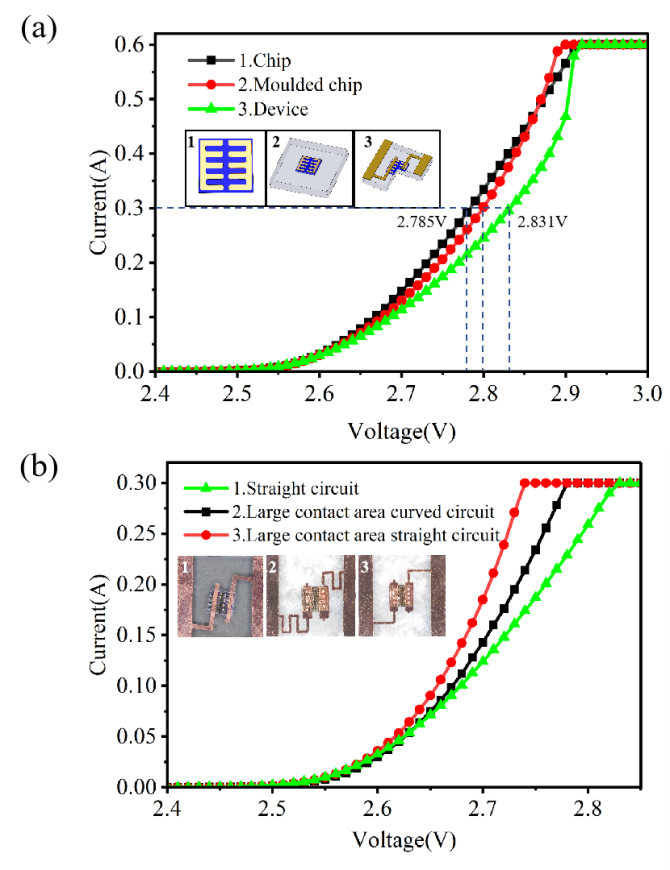

Fig8.(a)芯片、模压芯片和最终器件的电压-电流(V-I)特性。(b)三种不同RDL结构的电压-电流(V-I)特性。

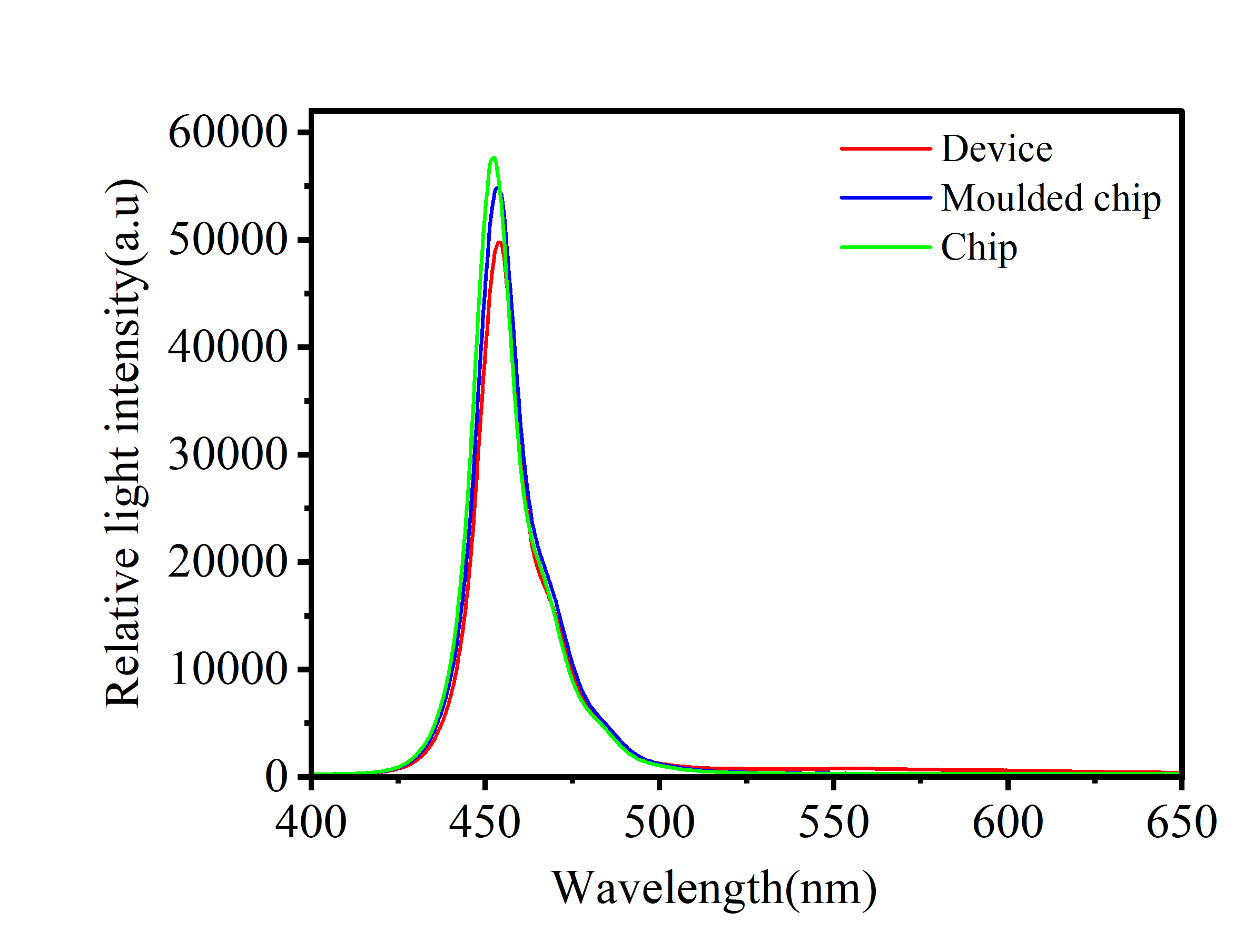

Fig9.芯片、模压芯片和器件在相同电压下的光谱曲线。

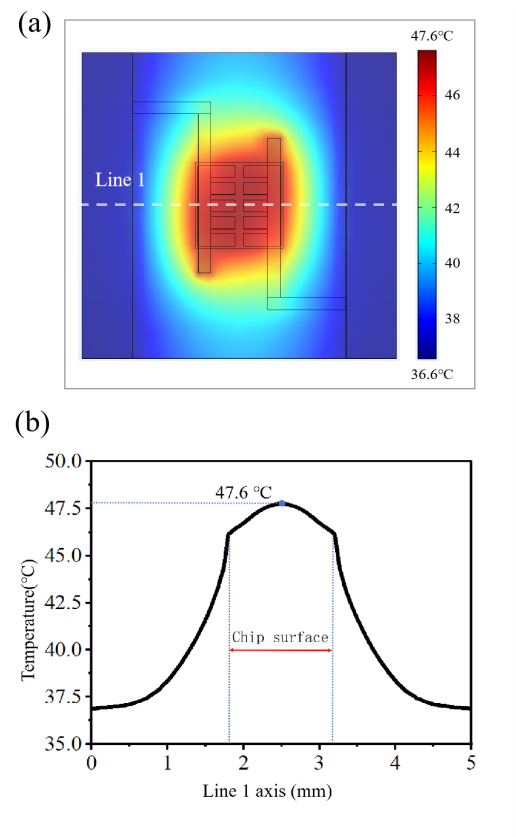

Fig10.(a)封装芯片的热分布云图。(b)图a中沿线1的温度分布曲线图。

Fig11.拉伸试验期间横向力和纵向力的变化。

结论

在这项研究中,我们提出了LDWL-FOP技术,旨在解决扇出封装过程中芯片转移步骤所造成芯片偏移的问题。RDL图案基于芯片的实际位置生成,可灵活补偿位置偏移,并确保RDL和芯片电极之间的精确对准。当芯片的旋转角度达到±10°时,RDL与芯片电极保持高精度连接,保证LED优异的电气性能。制造了不同的RDL结构,展示了LDWL-FOP方法的高灵活性。LDWL-FOP对LED芯片光电性能的影响可以忽略不计。FOP可以确保LED的有效热管理,以防止芯片的过热故障。此外,FOP器件表现出约50 N的抗剪切破坏力,证明了其在恶劣环境应用中的潜力。该研究展示出LDWL-FOP方法用于Mini/Micro-LED芯片高可靠封装的潜力。