基本信息

联系方式:yangsimei@scut.edu.cn

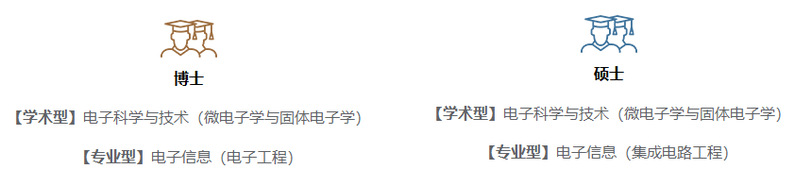

招生专业

招生/招聘信息:热烈欢迎对软硬件协同设计、设计空间搜索、多核系统建模仿真、数字集成电路设计感兴趣的本科生、硕士生、博士生和博士后加入课题组。简历请发送至邮箱:yangsimei@scut.edu.cn

Openings: We are looking for self-motivated undergraduate students, graduate students and postdocs who have passion in studying hardware-software codesign, Design Space Exploration, system-level modeling and simulation for multi-/many-core system, digital IC, etc.

个人简介

杨斯媚博士,2020年毕业于法国南特大学综合理工学院,随后在比利时欧洲微电子中心从事博士后和研究员工作共40个月。现任华南理工大学微电子学院副教授,硕士/博士生导师,主要从事软硬件协同设计、设计空间搜索、多核处理器的映射调度、大规模系统建模和仿真等领域研究。

Dr. Simei YANG received her Ph.D degree from IETR UMR CNRS 6164, Polytech Nantes, Université de Nantes, France, in 2020. After that, she worked in Belgium for 40 months as a postdoc and researcher. She is currently the associate professor of School of Microelectronics, South China University of Technology. Her research interests include Hardware-Software Codesign, Design Space Exploration, run-time resource management for multi/many-core systems, and system-level modelling and simulation of multi/many-core systems.

教育经历

2016/11-2020/06, 法国南特大学综合理工学院,多核嵌入式系统,博士

2014/09-2016/07,中山大学, 集成电路工程,硕士

2010/09-2014/07,中山大学, 微电子,学士

工作经历

2024/01-至今,华南理工大学,副教授,PI

2022/06-2024/01,比利时欧洲微电子中心 研究员

2020/10-2022/05,比利时欧洲微电子中心和鲁汶大学,博士后

研究方向

软硬件协同设计,设计空间搜索、多核系统资源调度,数字集成电路设计

授课课程

《Verilog与FPGA设计》或《数字集成电路原理与设计》

学术任职

科研项目

代表性科研成果

1.Yang S, Bhattacharjee D, Kumar V B Y, et al. AERO: Design Space Exploration Framework for Resource-Constrained CNN Mapping on Tile-Based Accelerators[J]. IEEE Journal on Emerging and Selected Topics in Circuits and Systems, 2022, 12(2): 508-521.

2.Yang S, Le Nours S, Real M M, et al. 0–1 ILP-based run-time hierarchical energy optimization for heterogeneous cluster-based multi/many-core systems[J]. Journal of Systems Architecture, 2021, 116: 102035.

3.Yang S, Le Nours S, Méndez Real M, et al. System-Level Modeling and Simulation of MPSoC Run-Time Management Using Execution Traces Analysis[C]//Embedded Computer Systems: Architectures, Modeling, and Simulation: 19th International Conference, SAMOS 2019, Samos, Greece, July 7–11, 2019, Proceedings 19. Springer International Publishing, 2019: 281-293.

4.Yang S, lez Nours S, mendez Real M, et al. Mapping and frequency joint optimization for energy efficient execution of multiple applications on multicore systems[C]//2019 Conference on Design and Architectures for Signal and Image Processing (DASIP). IEEE, 2019: 29-34.

5.Qiu, W., Chen, Y., Chen, D., Su, T., & Yang, S*. (2022). Run-Time Hierarchical Management of Mapping, Per-Cluster DVFS and Per-Core DPM for Energy Optimization. Electronics, 11(7), 1094.