基本信息

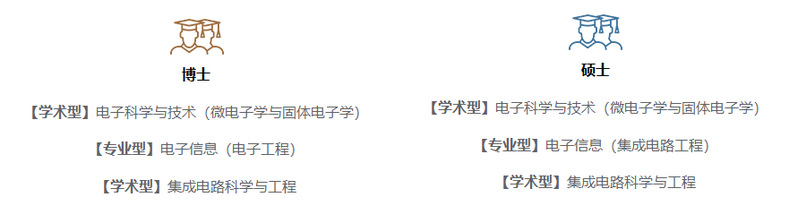

招生专业

个人简介

姚恩义,华南理工大学微电子学院副教授,博士生、硕士生导师,广州市创新创业团队引进项目核心成员,2016年于新加坡南洋理工大学电气与电子工程学院获得哲学博士学位,2016至2020年就职于华为技术有限公司,担任高级工程师,获批“深圳市海外高层次人才”称号,主要研究方向为新型智能计算芯片设计,近年来在IEEE TCAS-I,IEEE TCAS-II、IEEE TCAD、IEEE TVLSI、IEEE TBCAS等高水平期刊和顶级会议上发表论文50余篇。长期担任多个国际知名高水平期刊(如IEEE TCAS-I、TCAS-II、TVLSI、SSCL等)的审稿人以及IEEE APCCAS、ICTA 等知名国际高水平学术会议的技术委员会(TPC)委员。中国计算机协会(CCF)集成电路设计专委执行委员,以及中国计算机协会青年计算机科学家论坛(CCF YOCSEF)广州分论坛学术委员(2022-2025)。目前主持及参与国家自然基金、广东省自然基金、教育部重点实验室课题等10余项科研项目。研究团队核心特色在于聚焦新型智能计算芯片及领域专用硬件加速器架构研究,同时开展大规模ASIC芯片设计和FPGA原型开发工作,所指导博士生于2025年获批首届中国科协青年人才托举工程博士生专项计划。

Yao Enyi is an Associate Professor at the School of Microelectronics, South China University of Technology. He serves as a supervisor for both doctoral and master's students and is a core member of the Guangzhou Innovation and Entrepreneurship Team Introduction Project. He obtained the Ph.D. degree from the School of Electrical and Electronic Engineering at Nanyang Technological University in Singapore in 2016. From 2016 to 2020, he worked at Huawei Technologies Co., Ltd. as a Senior Engineer and was awarded the title of “Shenzhen Overseas High-Level Talent.” His main research direction is the design of new intelligent computing chips. In recent years, he has published over 50 papers in high-level journals and top conferences such as IEEE TCAS-I, IEEE TCAS-II, IEEE TCAD, IEEE TVLSI, and IEEE TBCAS.

He has long served as a reviewer for several internationally renowned high-level journals (such as IEEE TCAS-I, TCAS-II, TVLSI, SSCL) and as a Technical Program Committee (TPC) member for well-known international high-level academic conferences like IEEE APCCAS and ICTA. He is an executive committee member of the Integrated Circuit Design Special Committee of the China Computer Federation (CCF) and an academic committee member of the CCF Young Computer Scientist Forum (CCF YOCSEF) Guangzhou sub-forum (2022-2025). Currently, he is leading and participating in more than ten research projects, including the National Natural Science Foundation, Guangdong Natural Science Foundation, and key laboratory projects from the Ministry of Education. The core feature of his research team focuses on the research of new intelligent computing chips and domain-specific hardware accelerator architectures, while also conducting large-scale ASIC chip design and FPGA prototype development. The doctoral students he supervises have been approved for the first “China Association for Science and Technology Young Talent Support Project” doctoral program in 2025.

教育经历

2011.08-2015.07 新加坡南洋理工大学 博士

2007.08-2011.07 哈尔滨工业大学 学士

工作经历

2021.01至今 华南理工大学微电子学院 副教授

2016.12-2020.12 华为技术有限公司 高级工程师

2015.10-2016.11 新加坡南洋理工大学 博士后研究员

研究方向

面向组合优化的专用求解器芯片、Ising退火处理器芯片设计

人工智能芯片设计、类脑计算芯片设计、存算一体

后量子加密、全同态加密芯片设计

学术任职

中国计算机协会集成电路设计专委执行委员

中国计算机协会青年计算机科学家论坛(CCF YOCSEF)广州分论坛学术委员(2022-2025)

IEEE TCAS-I、TCAS-II、TVLSI、SSCL等期刊审稿人

IEEE TCAS-II客座编辑(2023)

2022 IEEE APCCAS会议人工智能电路与系统分论坛主席

2022、2023 ICTA会议分论坛主席

科研项目

1.国家自然科学基金-面上项目,面向大规模组合优化问题的高性能Ising处理器芯片关键技术研究,2026-01至2029-12,在研,主持;

2.广东省自然科学基金-面上项目,基于存算一体的组合优化问题硬件加速器芯片关键技术研究,2023-01至2025-12,在研,主持;

3.广东省自然科学基金粤穗联合基金, 面向边缘计算的可在线学习类脑计算芯片关键技术研究,2022-10至2025-09,在研,主持;

4.广州市创新创业团队引进项目,2024-12至2029-12,在研,课题负责人;

5.广州市基础与应用基础研究项目,基于伊辛模型的新型智能计算芯片关键技术研究, 2022-04至2024-03,结题,主持;

6.人工智能教育部重点实验室课题,新型类脑计算芯片关键技术研究,2022-12至2024-11,结题,主持;

7.广东省光电信息处理芯片与系统重点实验室课题,基于存内计算的新型类脑计算芯片关键技术研究, 2023-05至2023-11,结题,主持;

8.教育部产学合作协同育人项目,基于飞腾处理器的数字集成电路设计课程建设,2022-10至2023-09,结题,主持;

9.企业委托技术开发项目,多次可编程非易失存储器设计,2024-01至2024-12,结题,主持;

10.深圳市科技重大专项项目,亿门级通用FPGA芯片及配套EDA工具关键技术研发,2024-11至2026-11,在研,参与;

代表性科研成果

详情请浏览:

https://scholar.google.com/citations?hl=zh-CN&user=JNbWKlIAAAAJ&view_op=list_works&sortby=pubdate

[1]D. Jiang, X. Wang, Z. Huang, L. Kang, S. Yang and Enyi Yao*, “A Spin Scale-Aware Self-Adaptive Ising Annealing Processing Architecture for Combinatorial Optimization Problems,” IEEE Transactions on Circuits and Systems I: Regular Papers, 2025.

[2]K. Lai, Enyi Yao, Z. Li, Y. Yang, “A High-Density eDRAM Macro With Programmable Sense Amplifier and TG-Shifter for Logical-Instruction-Based In-Memory Computing,” IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 33, no. 7, pp. 2069-2073, July 2025.

[3]Z. Huang, Y. Zhang, X. Wang, D. Jiang and Enyi Yao*, “DCAP: a scalable decoupled-clustering annealing processor for large-Scale traveling salesman problems,” IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 71, no. 12, pp. 6349-6362, 2024.

[4]Y. Zhang, X. Wang, G. Fan, Y. Cao, Y. Liu, Y. Yang and Enyi Yao*, “An Ising Model-Based Parallel Tempering Processing Architecture for Combinatorial Optimization,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 43, no. 12, pp. 4572-4584, Dec. 2024.

[5]D. Jiang, X. Wang, Z. Huang, Y. Yang and Enyi Yao*, “A Network-on-Chip-Based Annealing Processing Architecture for Large-Scale Fully Connected Ising Model,” IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 70, no. 7, pp. 2868-2880, 2023.

[6]Z. Huang, D. Jiang, X. Wang and Enyi Yao*, “An Ising Model-Based Annealing Processor With 1024 Fully Connected Spins for Combinatorial Optimization Problems,” IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 70, no. 8, pp. 3074-3078, 2023.

[7]Y. Huang, G. Fan, J. Mai, W. Jiang, J. Hu and Enyi Yao*, “A Post-Quantum Encryption Mechanism Based on Convolutional Neural Network Accelerator,” IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 71, no. 8, pp. 3945-3949, Aug. 2024.

[8]Y. Cao, Y. Ni, Y. Zhou, H. Li, Z. Huang and Enyi Yao*, “An Auto Chip Package Surface Defect Detection Based on Deep Learning,” IEEE Transactions on Instrumentation and Measurement, vol. 73, pp. 1-15, 2024.

[9]Y. Yang, T. Yin, J. Liu and Enyi Yao*, “A low-cost digital calibration scheme for high-resolution SAR ADC using Adaptive-LMS,” Electron. Lett., vol. 58, no. 25, pp. 949-951, 2022.

[10]Y. Cao, Y. Zhou, Z. Zhang and Enyi Yao*, “Representation Learning Method for Circular Seal Based on Modified MLP-Mixer,” Entropy, vol. 25, no. 11: 1521, 2023.

[11]Y. Cao, H. Li, L. Han, X. Zhao, X. Pan and Enyi Yao*, “AccFlow: Defending against the Low-Rate TCP DoS Attack in Drones,” Applied Sciences, vol. 13, no. 21: 11749, 2023.

[12]Z. Wu, Y. Cao, H. Waris, Enyi Yao* and D. Liang, “A lightweight real-time smartphone-based laser speckle contrast analyzer,” Optics Communications, vol. 543, 129613, 2023.

[13]J. Hu, X. Pang, D. Jiang, G. Fan and Enyi Yao*, “An SRAM Compute-in-Memory Based NTT Accelerator for CRYSTALS-KYBER,” IEEE International Symposium on Circuits and Systems (ISCAS), 2025, accepted.

[14]J. Mai, F. Zhao, Z. Huang, Y. Yang, S. Jiang and Enyi Yao*, “HSCIM: A High Security Compute-in-Memory Architecture with PUF Based on TST-MRAM,” IEEE International Symposium on Circuits and Systems (ISCAS), 2025, accepted.

[15]Z. Wu, Z. Luo, J. Mai and Enyi Yao*, “An Efficient and Flexible Hybrid Implementation of Pair and Triplet-Based STDP Learning,” IEEE International Symposium on Circuits and Systems (ISCAS), 2025, accepted.

[16]Y. Zhang, X. Wang, D. Jiang, Z. Huang, G. Fan and Enyi Yao*, “A Parallel Tempering Processing Architecture with Multi-Spin Update for Fully-Connected Ising Models,” Design, Automation & Test in Europe Conference & Exhibition (DATE), Valencia, Spain, pp. 1-6, 2024.

[17]Y. Huang, J. Mai, W. Jiang and Enyi Yao* “A Trusted Inference Mechanism for Edge Computing Based on Post-Quantum Encryption,” IEEE International Symposium on Circuits and Systems (ISCAS), Singapore, pp. 1-5, 2024.

[18]Z. Huang, X. Wang, D. Jiang, Y. Huang and Enyi Yao*, “An Annealing Processor based on 1k-Spin Fully-Connected Ising Model for Combinatorial Optimization Problems,” IEEE International Symposium on Circuits and Systems (ISCAS), Monterey, CA, USA, pp. 1-5, 2023.

[19]D. Jiang, X. Wang, Z. Huang, Y. Huang and Enyi Yao*, “A Scalable Annealing Processing Architecture for Fully-Connected Ising Models,” IEEE International Symposium on Circuits and Systems (ISCAS), Monterey, CA, USA, pp. 1-5, 2023.

[20]Z. Luo, J. Mai and Enyi Yao*, “OTFC-LSTM: An Efficient Design of LSTM Accelerator based on On-The-Fly CORDIC,” IEEE 6th International Conference on AI Circuits and Systems (AICAS), Abu Dhabi, United Arab Emirates, pp. 372-376, 2024.

[21]X. Sun, Y. Zhang, Y. Jiang, Z. Li, B. Han, J. Mai, Z. Luo and Enyi Yao*, “HLC: A Hardware-friendly Quantization and Cache-based Accelerator for Transformer,” IEEE 6th International Conference on AI Circuits and Systems (AICAS), Abu Dhabi, United Arab Emirates, pp. 447-451, 2024.

[22]Y. Zhang, X. Wang and Enyi Yao*, “An Area-Efficient Ising Machine based on Parallel Stochastic Cellular Automata Tempering,” IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), Hangzhou, China, pp. 120-121, 2024.

[23]J. Hu and Enyi Yao*, “A Configurable, Parallel and High-Performance NTT/INTT Accelerator for Post-Quantum Cryptosystems,” IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), Hangzhou, China, pp. 82-83, 2024.

[24]X. Wang, D. Jiang, Y. Zhang, H. Kang and Enyi Yao*, “A Genuine-Equilibrium Monte Carlo Sampling-Based Effective Algorithm for Fully-Connected Ising Models,” IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), Hefei, China, pp. 72-73, 2023.